GerhardCadek New Contributor

New Contributor

3 months ago New Contributor

New ContributorHow-to generate dual-port (read/write) RAM with clock enables

Following Stratix® 10 Embedded Memory User Guide (2025.07.24) chapter 2.11.6 independent clock enables are supported for

- read/write clock mode

- input/output clock mode

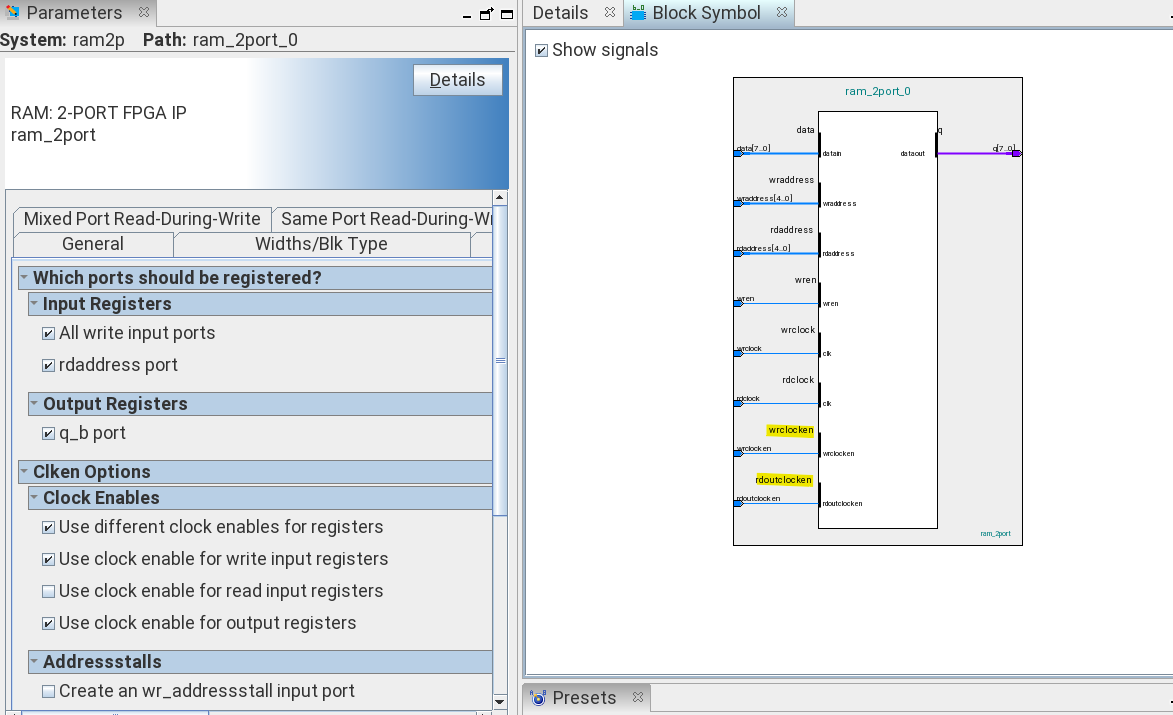

I start a "RAM 2-port" IP generation. I select "one read/write port" in the general tab and "dual clock use separate read and write clock" in the "Clks/Rd,Byte En" tab. Now I enable the clock enables in the "Reg/Clkens/Aclrs" tab "use clock for read input register" as well as same for "output registers". IP Parameter window immediuately shows an error:

Error: testram.ram_2port_0: Clock enable for read input registers is unavailable while using 'Dual clock: use separate read and write clocks' for Stratix 10 device family.

This is verified with Quartus Pro 18.1 and 25.3. Is this a bug of the software or the documentation?