Sai2403 New Contributor

New Contributor

3 months ago New Contributor

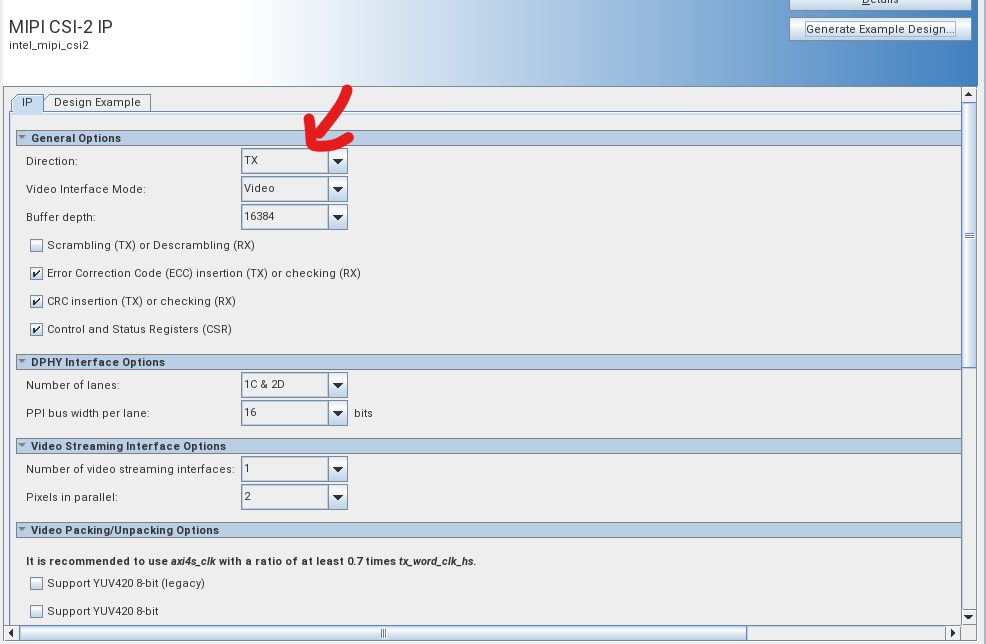

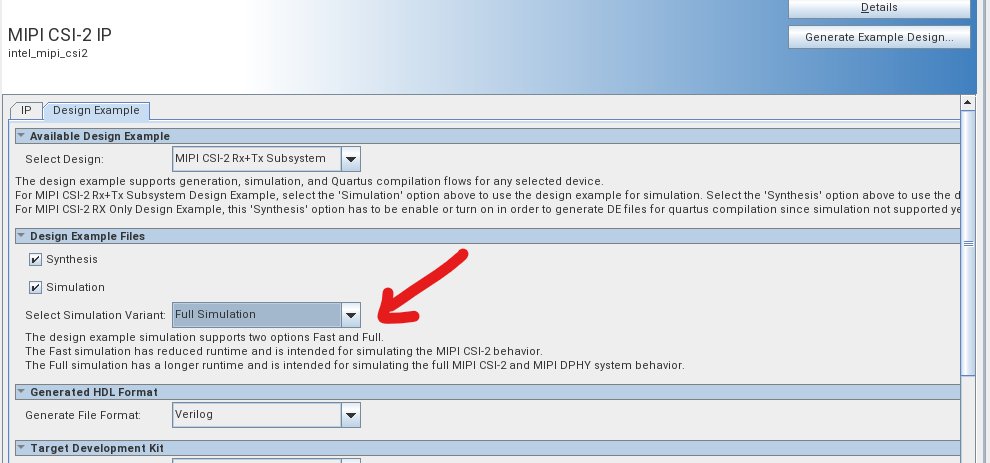

New ContributorRegarding MIPI CSI 2 TX

Hi, In my Project, I have to generate test pattern data and send it to MIPI CSI 2 via AXI stream, and MIPI CSI 2 will send the pixel data to link_0 of MIPI DPHY IP , but when i try to simulate the design(includes MIPI CSI 2 and MIPI DHPY IP interconnected), mipi_dphy_0/LINK0_CK_Stopstate is constantly high, I guess this signal is supposed to go low after T INT time, and also ready Singal from axi_stream is asserted low after being high for three clock cycles, i didn't understand why.

Any help is appreciated.