New Contributor

New ContributorStratix 10 Transceiver PHY bonding and multiple TX PLL clock inputs (for DisplayPort TX)

We are using a Stratix 10 L-Tile/H-Tile Transceiver Native PHY to implement a DisplayPort TX and RX.

The transceiver is set as Basic (Enhanced PCS), TX/RX Duplex. The TX PMA is set as Non bonded, with 2 TX PLL clock inputs.

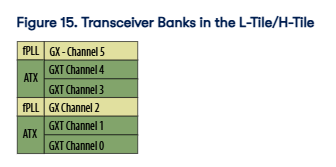

One of the TX PLL clock inputs is driven by a fPLL and used for rates from 1.62G up to 13.5G. The other clock input is driven by two ATX PLLs (one working as Main PLL, the other as GXT Clock Buffer) and used for 20G rate. This works ok.

The problem is that DisplayPort requires controlled skew between the 4 TX channels. That is, we need bonding for the 4 TX channels. If we set the TX PMA as "PMA only bonding" it seems we cannot have anymore multiple TX PLL clock inputs but just a single one.

How can we use the Stratix 10 PHY to implement DisplayPort TX rates from 1.62G up to 20G with 4 bonded channels (= 4 lanes)?

Hi,

After consulting with our DisplayPort (DP) IP experts, it appears that our DP is currently not operating in bonded mode for multi‑lane support. You may want to explore our DP IP.

Please let me know if you have any questions or concerns. Thank you.