New Contributor

New ContributorAgilex5 - Bridge AXI F2H - read transactions

Hi, we are using in our design the bridge F2H between FPGA and HPS, which is a bus ACE5lite 256bits. Several masters AXI 64bits in our design will contact it via an interconnect.

In Write, no problem, we can attaquer this interface in « narrow transfers » 64b over 256b, in conformity with ARM specification.

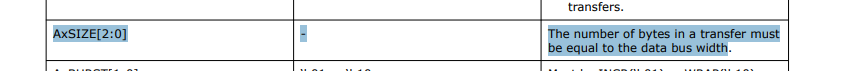

But in READ, the SoC user manual (814346, 2026.01.09) says §11.5.1 :

« The HPS F2H interface has a fixed data size of 256-bits. This interface allows for narrow burst sizes less than 256-bits However, if a fabric initiator generates a transfer narrower than the interface width (i.e., less than the 256-bits wide data and a nonzero burst size), there is no guarantee that the HPS F2H interface will respond with narrower data aligned on non-256-bit boundaries of the 256-bit data bus. For example, if ARADDR = 0x0010_0000, ARSIZE = 0x4, and ARLEN = 0x3, the HPS F2H interface returns two beats of 32 bytes per beat followed by two null cycles, instead of four beats of 16 bytes per beat. Altera recommends that you add width adaptation interconnect logic between the fabric initiator and the HPS F2H interface to ensure that the narrow-width data is packed/unpacked properly.”

« the HPS F2H interface returns » : means it is sure that… , we will be able logic tranlation 256>64 considering that data returned on RDATA bus will fill all width of 256b (if enough read bytes of course).

If “there is no guarantee…” is correct, it is a problem as there is no Read Strobe with bus RDATA in AXI spécification ; and we can not determine which bytes of which BEATs of transfert have to be considered.

Last possible interpretation : the ‘width adaptation interconnect logic’ recommanded by Altera concerns more the transformation of ARADDR/ARSIZE/ARLEN by our interconnect at bridge input (AR* parameters are requests of read sent by our masters should be translated by interconnect before to be presented to bridge).

Can you tell me the right meaning ?

Thanks and regards