Forum Discussion

Frequent Contributor

Frequent ContributorHi ohfpga1

Apologies for the long delay in the response to your question.

From the HPS reference manual document for Agilex 5, the recommendation is that width adaptation logic is required to handle 256-bit data packing and unpacking at the RDATA interface, not merely to translate ARADDR/ARSIZE/ARLEN parameters before presenting requests to the bridge. The F2H bridge returns data aligned to 256-bit boundaries (with potential null cycles for narrow requests) rather than true narrow beats, and requires AxSIZE to match the full 256-bit data bus width

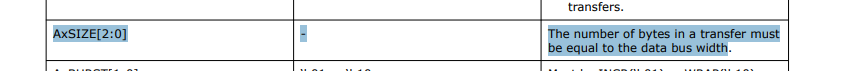

in the documentation also mentions about the rw/wr data must be equal to the data bus width

Therefore, the width adapter logic must intercept the 64-bit master's request and translate the ARADDR, ARSIZE (forcing it to 0x5 for 256-bit), and ARLEN before presenting it to the F2H bridge on the request part.

As width adapter forced the bridge to perform a standard full-width 256-bit, the bridge will in turn will return 256-bit aligned beats. The adapter must now act as a downsizer, capturing that 256-bit RDATA beat, unpacking it, and slicing it into the expected 64-bit beats with the correct valid/last signaling for the original master.

In short the F2H bridge does not natively support standard AXI narrow reads thus width adaptation logic is needed to ensure the bridge is operating at 256bit (convert narrow AxSIZE request to 256bits) and to handle the unpacking of 256bit RDATA.

Hope it addresses your question on the AXI F2H.

Thanks

Regards

Kian