ohfpga1 New Contributor

New Contributor

13 days ago New Contributor

New ContributorTimings eMMC

Hi,

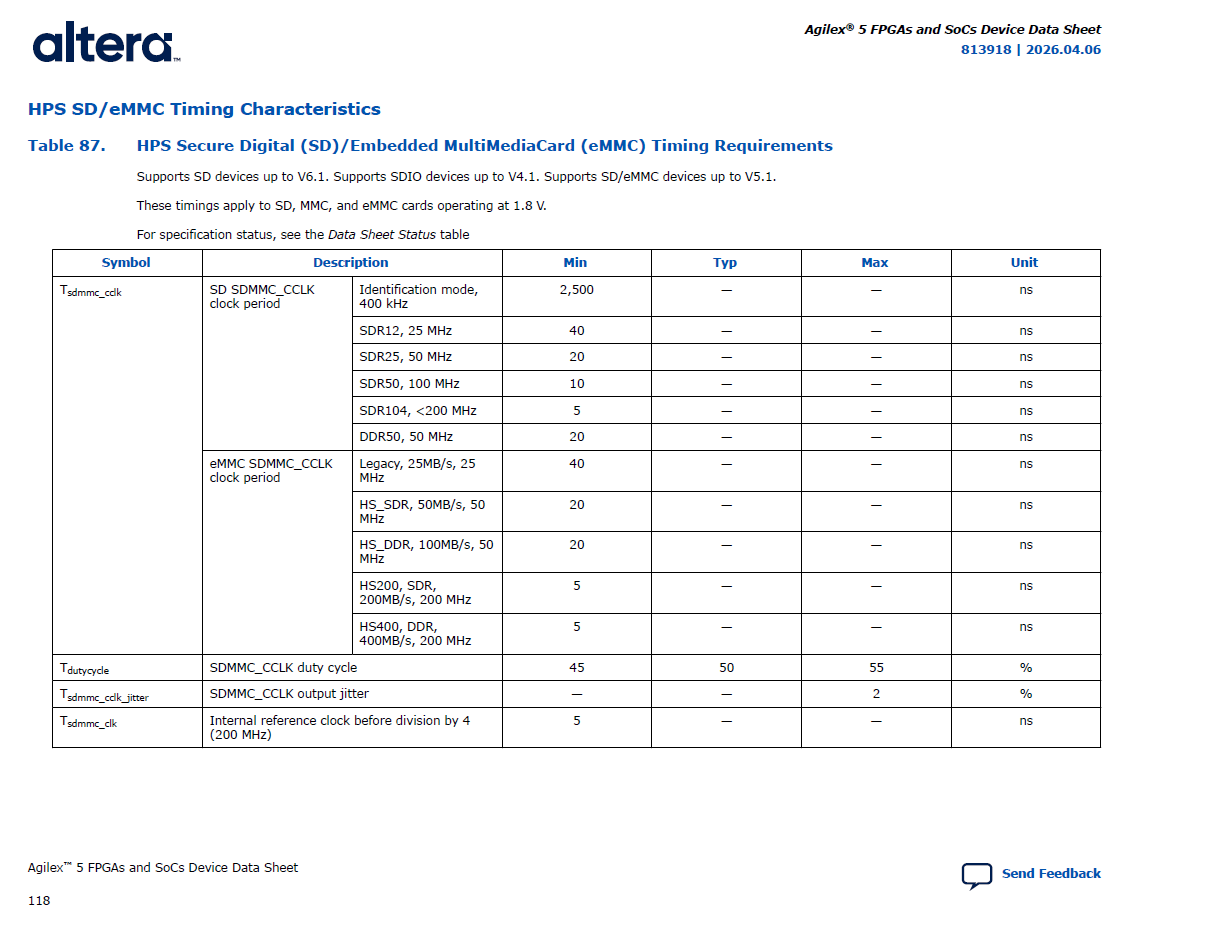

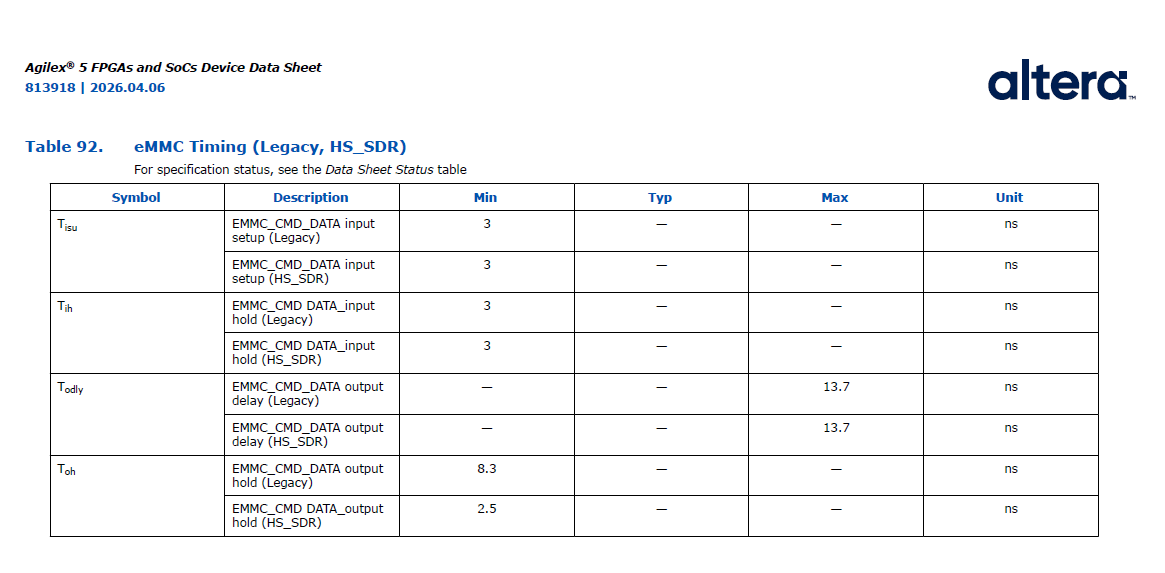

latest datasheet of SoC « 813918/2026.01.05 » lists in paragraph « HPS SD/eMMC Timing Characteristics » the constraints of eMMC, applicable to memory component but does not define any timing data in input/output of SoC.

There is no Tco min/max of CMD/DATA at SoC output, as well as Tsetup/hold of CMD/DATA at SoC input.

Can you provide Tco and Tsetup/hold for eMMC usage (Legacy, HS_SDR, HS_DDR, HS200, HS400) ?

thanks