New Contributor

New ContributorAgilex 5 EMIF-LPDDR4, AXI4 Read-Write Starvation Issue

Hello, I have a Agilex 5 design (based on the Terasic DE25_Nano) implementing the LPDDR4-EMIF.

My own IP (acting as a AXI4 Manager) is connected to the AXI4 Subordinate port of the EMIF to read and write onto the LPDDR.

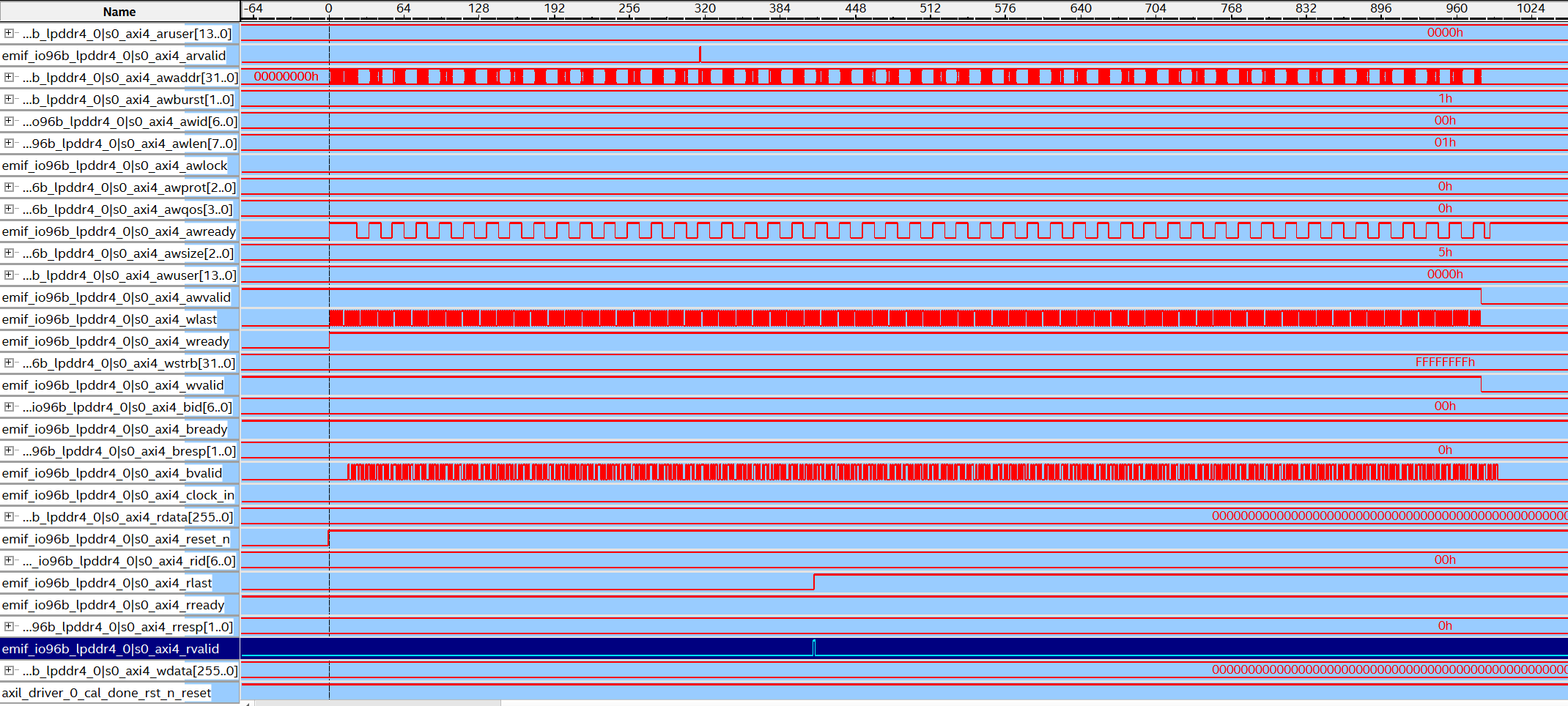

All is working perfectly, but in some R/W pattern cases where the write channel issues many consecutive commands, the Read channel is starved until the end of the write sequence of commands, which means no valid data are received before a very long (unacceptable) time.

Obviously the EMIF gives the priority to the write channel which lead to read starvation.

Regarding the EMIF Parameters Settings, I tested the three "Controller Performance Profiles" without any success. I also tested several set of values for the "Data Bus Turnaround Times" settings without any success too.

Ideally, I would expect either disabling Reordering or configuring a Starvation counter limit, but these parameters do not exist in the Agilex 5 EMIF IP. As a remark, I noticed these settings (Enable Reordering + Starvation limit) exist in the Agilex 7 EMIF IP.

Regarding the External Memory Interfaces (EMIF) IP User Guide for Agilex 5 FPGAs and SoCs, section "Features of the Agilex 5 Hard Memory Controller" Table 30, I noticed there is a parameter named "Starvation counter" but there is no explanation how to configure it.

In summary, I do not see any way to have control over Reordering/Starvation with Agilex 5 EMIF-LPDDR4.

Thank you in advance for any suggestion. Regards