New Contributor

New ContributorF-Tile xcvr placement on DK-DEV-AGF023FA

I have an Agilex 7 FPGA F-Series Development Kit 2xF-Tile DK-DEV-AGF023F. I have 1 F-Tile working with PCIe Gen4x16, and want to use the second for 400Gb Ethernet.

I have used the F-Tile channel placement tool, which results in a valid placement. See attached.

I have been plagued with placer message such as the following.

Error(22811): The specified block ftile_eth|u0|eth_f_0|hip_inst|per_xcvr[0].x_bb_f_ux|x_bb_f_ux_rx cannot be placed at the location fgt_q2_ch0_rx as the block requires stream(s) [0] in an Ethernet 400g block but the location only supports stream(s) [7, 11, 13, 14].

I have swapped bit orders and other trials, and they all lead to a similar error. Given the placement of the QSFPDD on the board, I need to used FGT Quads 2 and 3

I have also tried to use the 100G-4 F-Tile configuration, which move the FGT usage to Quad 1. And I result it the following error:

Error(22811): The specified block ftile_eth|u0|eth_f_0|hip_inst|per_xcvr[0].x_bb_f_ux|x_bb_f_ux_rx cannot be placed at the location fgt_q2_ch0_rx as the block requires stream(s) [0] in an Ethernet 100g block but the location only supports stream(s) [1, 2, 3].

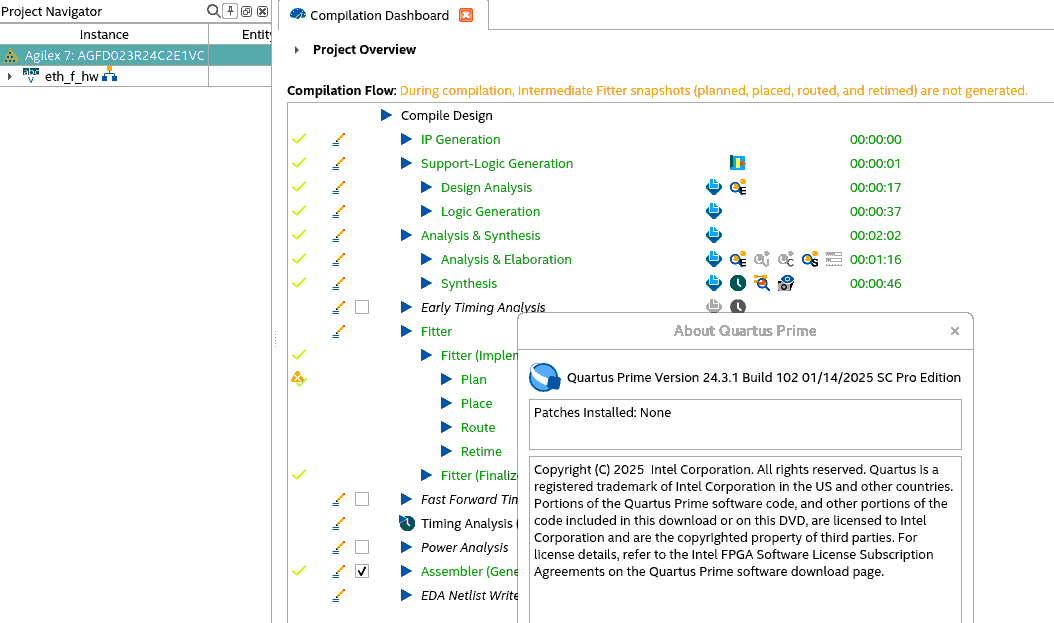

I have tried the example design, changing the device to the above board, but the build fails. Using Quartus 25.3.0

What is needed to move past these errors?

Thanks, Ed.